TPU Tensor блокTensor обработки)

Узнайте, как процессо Tensor Units (TPU) ускоряют машинное обучение. Научитесь оптимизировать Ultralytics для Edge TPU и облачного обучения для достижения максимальной скорости.

Tensor Unit (TPU) — это специализированная интегральная схема (ASIC), разработанная Google

специально для ускорения

вычислений в области машинного обучения (ML). В отличие от

процессоров общего назначения, которые обрабатывают широкий спектр вычислительных задач, TPU с самого начала разрабатывались для

оптимизации массивных матричных операций, которые являются основой

нейронных сетей. Эта специфическая направленность позволяет им

достигать исключительно высокой пропускной способности и энергоэффективности, что делает их краеугольным камнем современной

инфраструктуры искусственного интеллекта (ИИ),

особенно в экосистемеGoogle . Они играют

важную роль в сокращении времени, необходимого как для обучения сложных моделей, так и для выполнения

масштабных вычислений в реальном времени.

Архитектура и функциональность

Архитектура TPU значительно TPU от традиционных процессоров. В то время как стандартный

CPU центральный процессор) превосходно справляется с последовательными задачами и

сложной логикой, а

GPU графический процессор) использует

параллельные ядра для графики и общих вычислений, TPU

систолическую матричную архитектуру. Такая конструкция позволяет данным

проходить через тысячи умножителей одновременно, без доступа к памяти для каждой операции. Благодаря максимальной

вычислительной плотности и минимальной задержке TPU идеально подходят для сложных задач линейной алгебры, которые встречаются в

приложениях глубокого обучения (DL).

Это специализированное оборудование в значительной степени оптимизировано для таких фреймворков, как

TensorFlow и все чаще поддерживается

PyTorch, что позволяет разработчикам обучать массивные

базовые модели или развертывать эффективные периферийные

решения без полной переработки кодовой базы.

Различение блоков обработки

Понимание аппаратной среды имеет решающее значение для оптимизации

операций машинного обучения (MLOps).

-

CPU: универсальный «мозг»

компьютера, идеально подходящий для последовательной обработки, предварительной обработки данных и выполнения сложных логических операций. Часто используется для

конвейеров пополнения данных, но работает медленнее

при выполнении сложных матричных вычислений.

-

GPU: Изначально

созданные для рендеринга изображений, графические процессоры являются отраслевым стандартом для

обучения моделей благодаря своей универсальности и массивному

параллелизму. Они отлично подходят для обучения гибких моделей, таких как

Ultralytics .

-

TPU: специально разработанный ускоритель, который обеспечивает гибкость и высокую скорость tensor . Он

предназначен для максимального увеличения

FLOPS (операций с плавающей запятой в секунду), специально

для вычислений нейронных сетей, часто обеспечивая превосходную производительность на ватт для определенных крупномасштабных рабочих нагрузок.

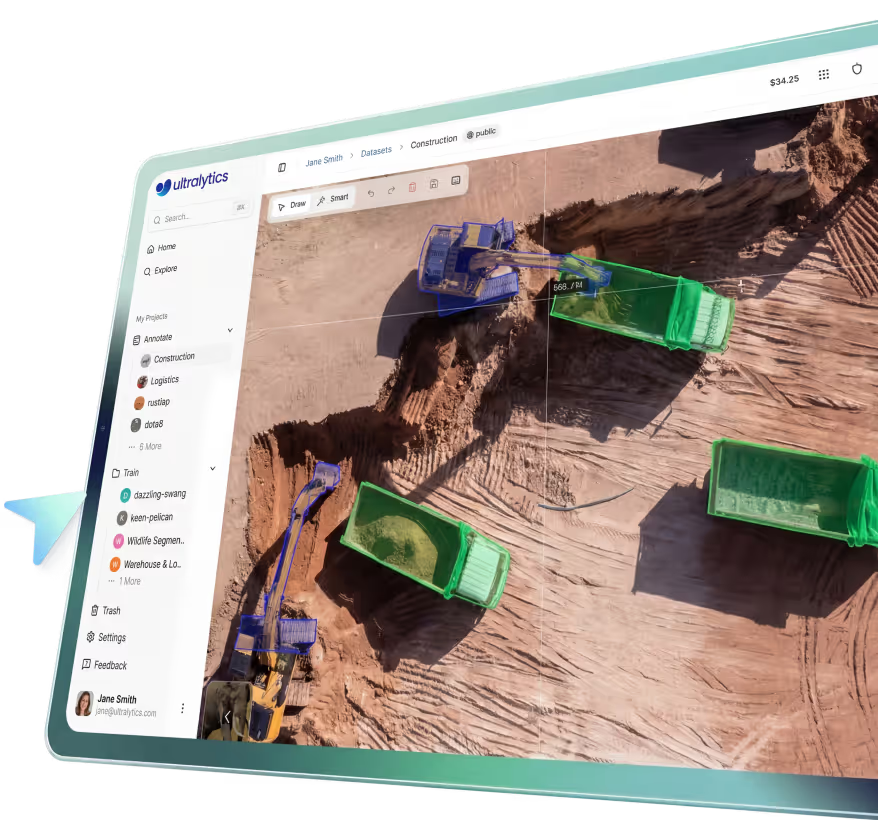

Применение в реальном мире

TPU развертываются в различных средах, от огромных облачных кластеров до крошечных периферийных устройств.

-

Обучение больших языковых моделей: Google огромные взаимосвязанные кластеры, известные как TPU , для

обучения огромных

больших языковых моделей (LLM), таких как

PaLM и Gemini. Эти системы могут обрабатывать петабайты

обучающих данных за долю времени, которое потребовалось бы

традиционному оборудованию, ускоряя прогресс в области

генеративного ИИ.

-

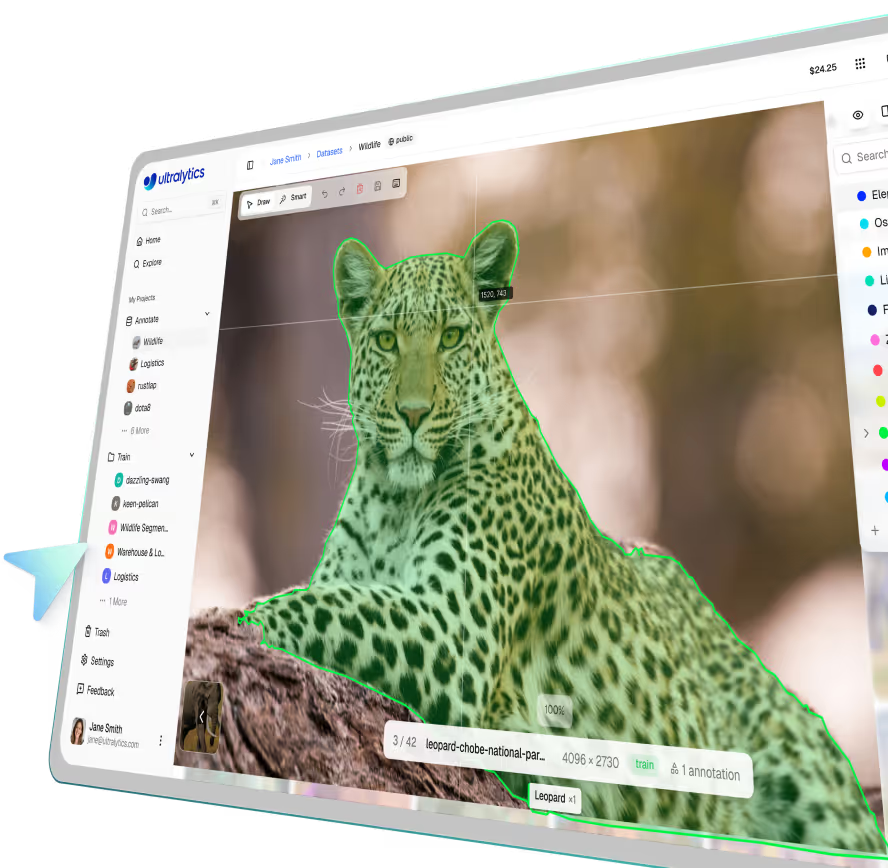

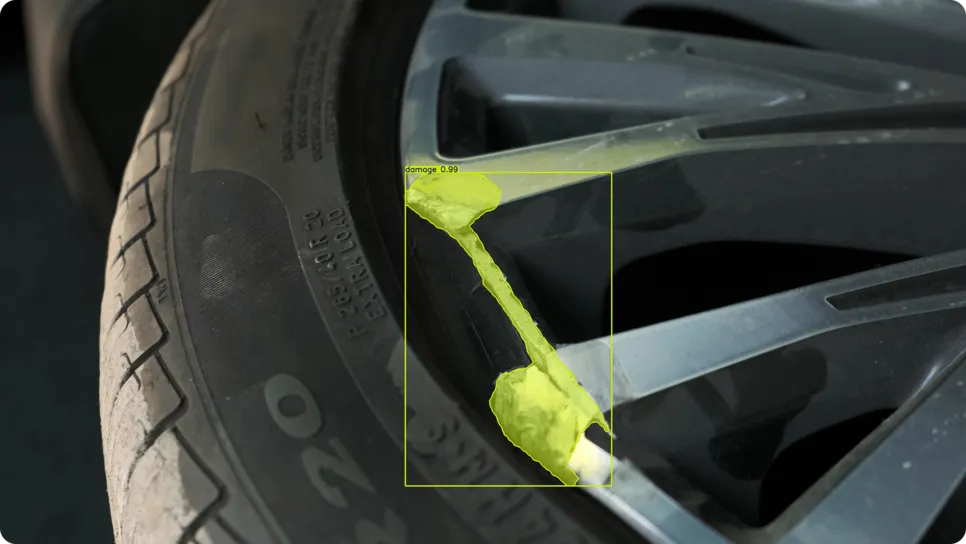

Edge AI и IoT: Coral Edge TPU обеспечивает такое

ускорение для устройств с низким энергопотреблением. Он позволяет эффективно

использовать приложения компьютерного зрения (CV), например,

запускать обнаружение объектов на производственной линии

для локальной идентификации дефектов. Это позволяет принимать решения немедленно, не полагаясь на подключение к облаку,

сохраняя пропускную способность и конфиденциальность.

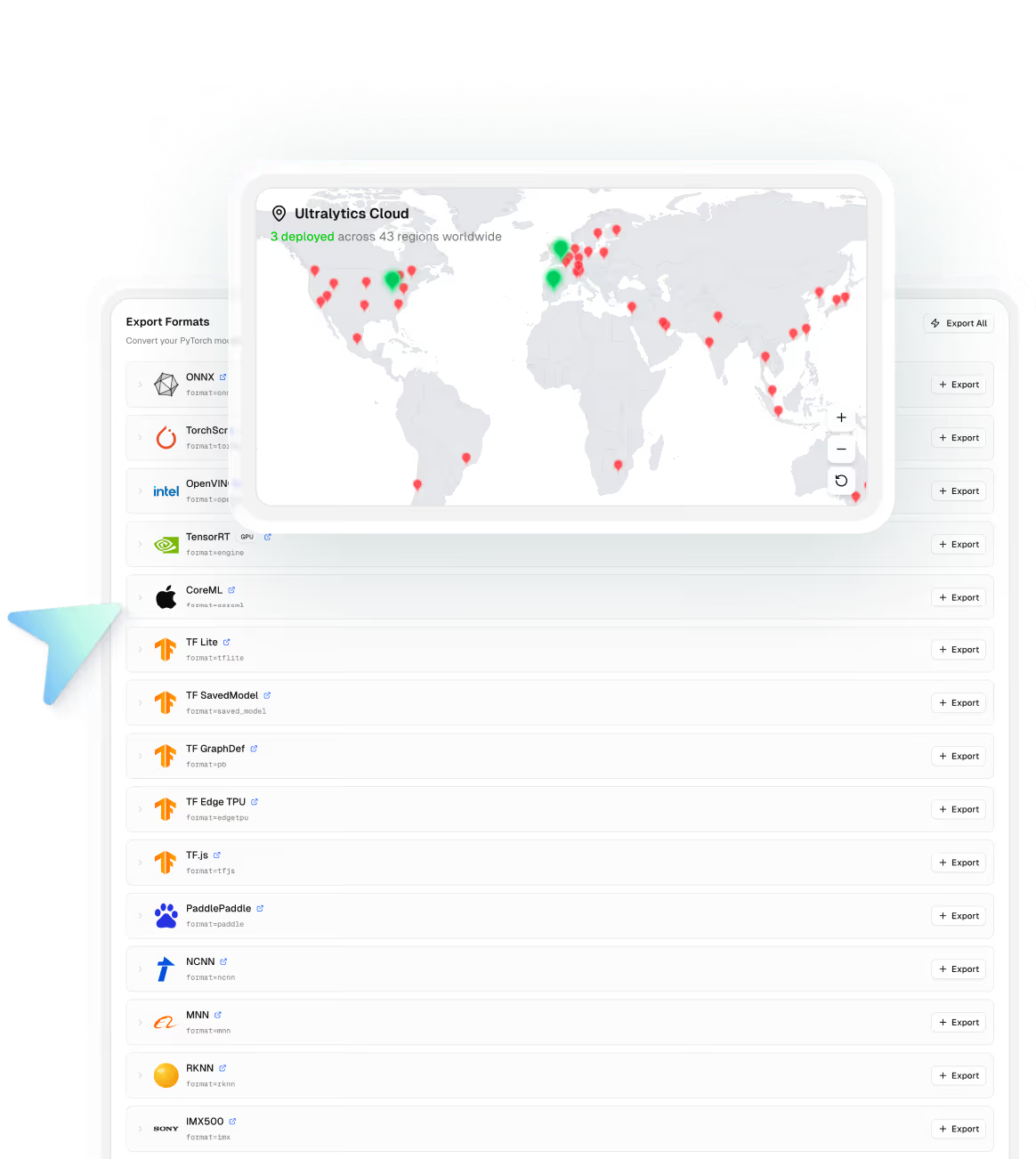

Использование TPU с Ultralytics

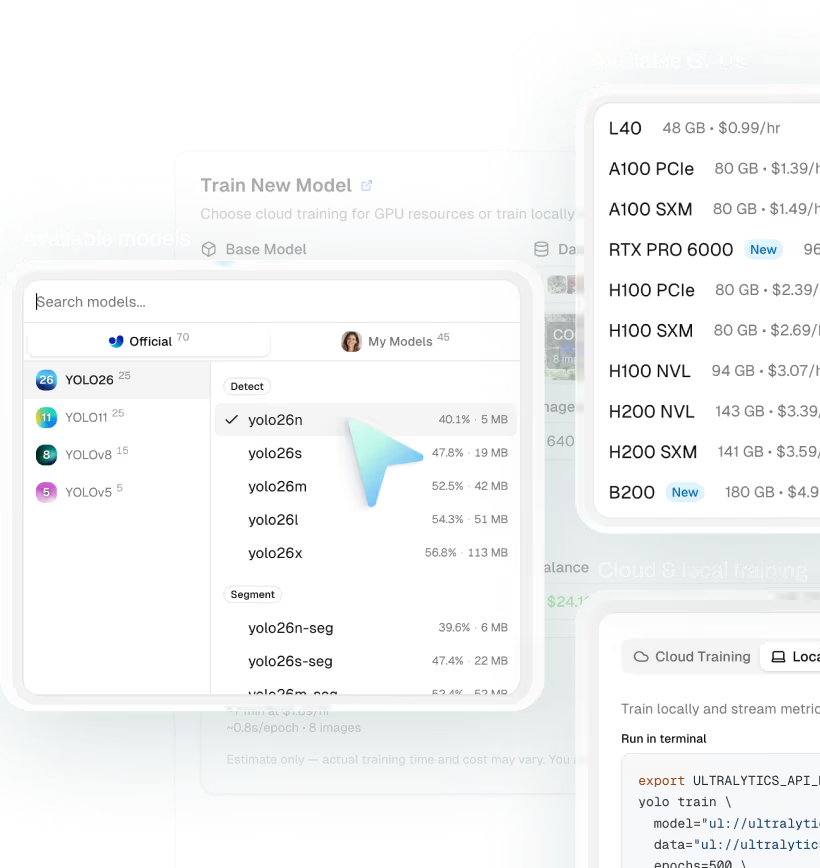

Разработчики могут использовать TPU для Ultralytics , особенно при использовании

Ultralytics для обучения в облаке или экспорта моделей для

развертывания на периферии. Например, Edge TPU требует, чтобы модели были квантованы и скомпилированы специально для его

архитектуры.

Следующий пример демонстрирует, как экспортировать модель YOLO26 в TFLite , что является обязательным шагом

перед компиляцией для Edge TPU:

from ultralytics import YOLO

# Load the latest lightweight YOLO26 nano model

model = YOLO("yolo26n.pt")

# Export the model to TFLite format

# This creates a '.tflite' file suitable for mobile and edge deployment

# Set int8=True for quantization, which is often required for Edge TPU performance

model.export(format="tflite", int8=True)

После экспорта модель можно дополнительно скомпилировать для Edge TPU

Edge TPU , что позволит ей эффективно работать

на таких устройствах, как Raspberry Pi с ускорителем Coral USB. Для получения более подробной информации о развертывании может быть очень полезно ознакомиться с

документацией TFLite

.